产品中心PRDUCTS

技术支持RECRUITMENT

江南体育官网ADC外部RC电路电阻和电容选取计算方法

2023-10-04 15:47:43

江南app下载s KE15内部有2个16bit SAR型ADC模块(以精度制胜),可以配合EDMA完美实现双ADC的同步采样,

相比很多以前需要MCU+外置ADC应用的场合来说,在成本上具有很大的优势。这些ADC通常都是SAR型的,相比较∑Δ类型的ADC来说通常速度要快很多,但是精度会差些,但已足够满足大部分的应用。然而想要在实际应用中达到标称的精度,仅仅依赖ADC模块本身是不够的,实际的测量精度还会受到诸多外在因素的影响,例如:

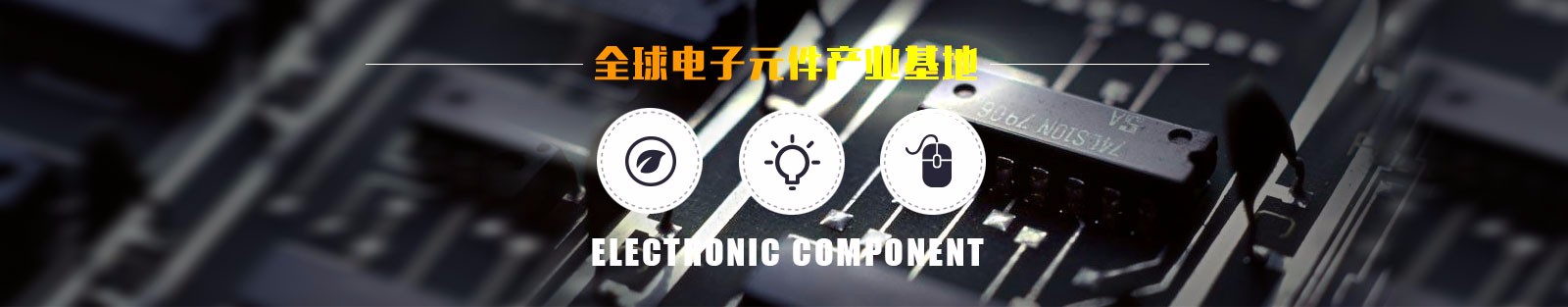

但是在实际应用中发现,ADC引脚外部的RC电路的电阻电容的取值对ADC的性能影响比较大,如有客户反馈在ADC采样期间会在ADC输入端观察到严重的电压扰动(电压跌落/电压尖峰),如下图1 所示,从而影响实际采样精度。

这种现象在多通道顺序采样,且前后两个连续采样通道信号电压差比较大时,现象会更加明显,因为ADC引脚的RC重新充电需要时间,这种扰动来源于SAR型ADC内部固有的采样电路,是不可避免的。

那既然无法避免,如何采取措施避免这种扰动对ADC采样的影响呢,尽可能的提高ADC的精度呢?答案是选择合适的采样时间和ADC采样引脚RC电路中电阻和电容的值,从原理上讲,其目的是保证在采样时间Taq内,采样电容Csh充分充电,使其两端电压与待测输入电压之间的差值达到一个可接受的范围内(通常在采样时间结束时刻,两者的差值不能超过满量程的 0.5LSB)。NXP AN4373文档对这块进行了深入的探讨,但是文章冗长不好理解,本文档尝试化繁为简先介绍RC值求取的公式理论推导,然后给出具体实例,方便理解。

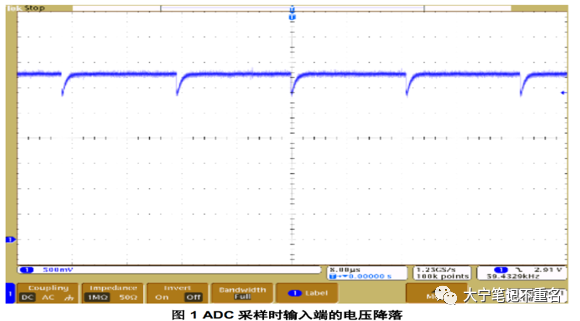

在一般的采样过程中,我们将采样时间内的待测输入信号当作一个有着恒定电压的直流电压源。通常设计人员会假设该电压源有着很大的内阻(即Rin>

Rsh)。在此假设下,采样电容充电期间将会出现两个明显不同的时间段,如图3所示。图中所绘为采样电容(红色)和输入电容(绿色) 两端的电压波形,其中,采样电容是指外部的电容,输入电容是指ADC内部电容。

图3所示为输入电容上的初始电压大于采样电容上的初始电压的情况(即Vcin>

Vcsh)。此时,输入电容两端的电压将出现电压降落。反之,当Vcin

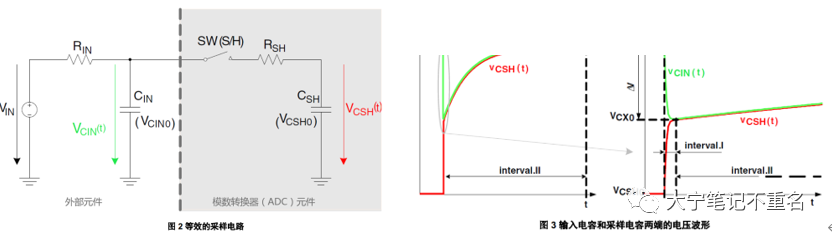

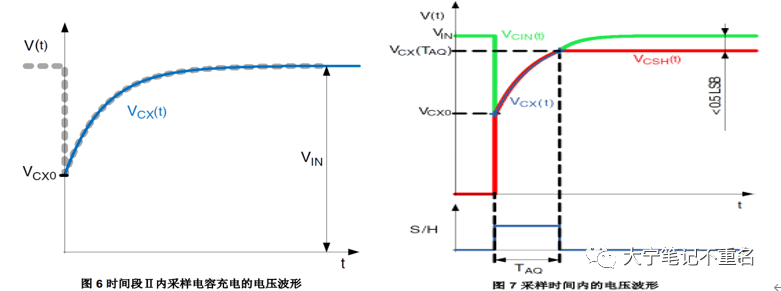

可以看到,图3中采样电容Csh两端的电压曲线可以划分为两个时间段,高输入阻抗阶段和低输入阻抗阶段,在高输入阻抗的情况下,时间段Ⅱ的曲线变化要比时间段Ⅰ缓慢许多。其中,时间段Ⅰ采样电容充电来自于外部输入电容Cin,时间段Ⅱ采样电容充电来自于外部流过Rin的外部电压输入因而江南体育官网,图2所示的等效电路可以根据时间段的不同划分为两个新的等效电路,如图4 所示。

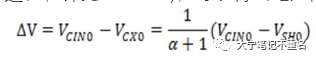

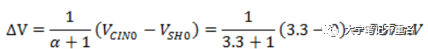

首先,先讨论时间段I内采样电容充电的波形,如上面图5所示。通过一系列公式推导(此处忽略推导过程,详见AN4373),可以得出电压降落/电压尖峰的幅度大小由后面的公式如下:

根据以上公式,可以发现输入电容与采样电容的比值越大,产生的电压降落(或电压尖峰)的幅度将越小。接着,讨论时间段II内采样电容充电的波形,其波形如下图6所示,而为了提高精度,我们的目标是保证图7中Vcx在Taq点采样的电压接近于真实值,也就是Vin-Vcx

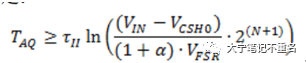

而想要使采样电容两端电压与实际待测电压之间的误差小于0.5LSB,则采样保持开关必须在采样 时间Taq内保持闭合,Taq需要满足:

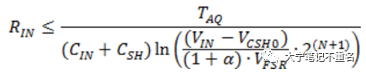

另外,如果采样时间Taq已经确定(对于Kinetis,软件可以设置),的变量包括Csh、Vfsr都是datasheet决定的,未知的两个变量分别为Cin和Rin,对于Kinetis,通常选择Cin为33pf,则对于设计者来说只需要考虑输入电阻Rin,其计算方法是:

Note:具体为何是33pF?AN4373文档表述为:参照数据手册8.2节中的建议,每个 ADC 输入端接不小于 33 pF的输入电容和不小于10 Ω 的输入电阻。需要注意的是,这个值是最小的值,实际选取可以适当大一些。

通常在选择设计外部RC元件时,我们常常犯这样的错误,希望通过增加输入电阻来降低输入电流,或是实现测量源和ADC之间的阻抗隔离。现在考虑这样的情况,如果增加到10 kΩ,使得在采样时间内不能充分充电,那么采样值也会不准确。所以,对于硬件设计者来说,问题的焦点集中在外部电阻的设计。

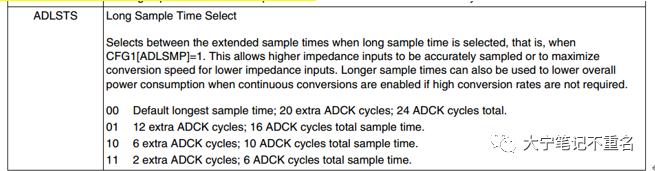

此处以Kinetis为例(同样使用其他配备SAR型ADC的MCU),ADC时钟为12M,16bit模式,采样时间设置尽可能的小(ADLSMP=0, ADLSTS=3,ADHSC=1),按照以上设置,ADC理论计算的总转换时间约为2.7 μs,采样时间Taq=6xADCK cycle=6x1/12=500ns,其中,为何乘数是6,请参见ADLSTS的配置,理论上可以设置更长,对精度有好处,但会影响速度,需要用户去平衡,本示例是按照最快速度去计算的。

按照以下公式片刻计算得出合适的Rin,Taq上面得出是500ns,从Kinetis datasheet上可以查到,输入电容Cadin或者Csh最大值为10pF, 数据手册中对Cin输入电容没有限制(数据手册中表述为Cas,选择为33pF,

计算的输入电阻最大取值表示我们可以在模拟输入端加上的最大电阻, 同时又不会损失采样的精度。如果选用超过最大取值的电阻,则将导致转换结果的错误。datasheet数据手册中给出的最大取值5kΩ,原因在于,其计算的配置与本例中给出的最大取值因条件不同而不同(数据手册中为 12/13-bit分辨率模式以及更低的ADC 时钟频率)。其电压跌落也能通过公式计算出来。

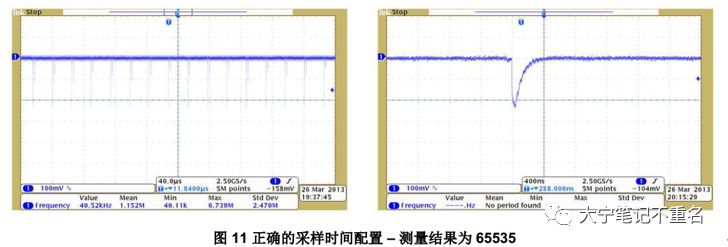

如图 11 所示,采样电容的充电过程在500 ns的采样时间内已经完成。因此,可以预见在结果寄存器中能够得到准确的转换结果。ADC0 模块的 DAD0 通道实际结果稳定在 65535(这与理想值的偏差为 0,即没有错误)。

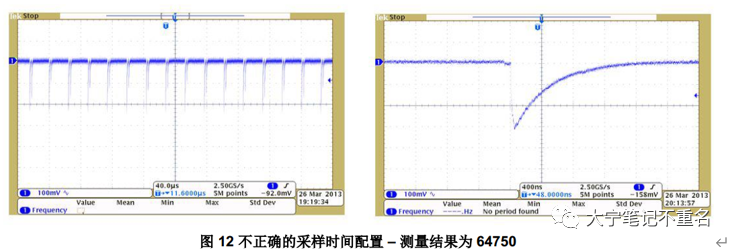

图12是将输入电阻从 1.1 kΩ 改为 5.1 kΩ 时的电压波形,从图中能明显观察到在 500 ns 的采样时间内,采样电容的充电过程还没有完成。因此, 结果寄存器中的转换结果不可能正确, ADC0模块的 DAD0 通道实际结果在 64750 附近变化。

在采样时间Taq内,采样电容Csh必须充分充电,使其两端电压与待测输入电压之间的差值达到一个可接受的范围内。通常在采样时间结束时刻,两者的差值不能超过满量程的 0.5LSB。

如果采用了高阻抗的输入电阻(更高的外部元件时间常数),则采样电容Csh将会首先由外部输入电容Cin的能量充电(更低的输入元件时间常数)。采样电容上的充放电过程导致了输入电容Cin两端电压的电压降落(或电压尖峰)。之后采样电容的充电过程由于较高的输入阻抗而变化的缓慢。

因此,外部 RC 元件的取值会从本质上影响ADC转换的精度,为了获得最佳的 ADC 性能,我们需要小心对待并设计外部 RC 元件,在选取采样时间时也必须参考采样电容充电的时间常数。其他需要满足的条件,详见器件的参考手册与数据手册。

示例中计算电阻R是基于33pF电容的,实际使用中,用户还需要对信号和外部可能的干扰信号的频率等综合考虑,但计算公式和选取思路是一样的,即在采样时间Taq内,采样电容Csh必须充分充电。

尽管示例中选取Kinetis MCU作为计算对象,但实际该计算方法也适用于其他的SAR型ADC

Note:本文所涉及到的参数名字可能和数据手册中的表述有所不同。例如:Rin=Ras(模拟源电阻),Cin=Cas(模拟源电容),Rsh=Radin(输入电阻),Csh=Cadin(采样电容),等式左边为本文所用符号,等式右边为数据手册用到的符号。