产品中心PRDUCTS

技术支持RECRUITMENT

江南体育为什么需要复位电路?漫谈复位reset

2024-01-22 08:46:52

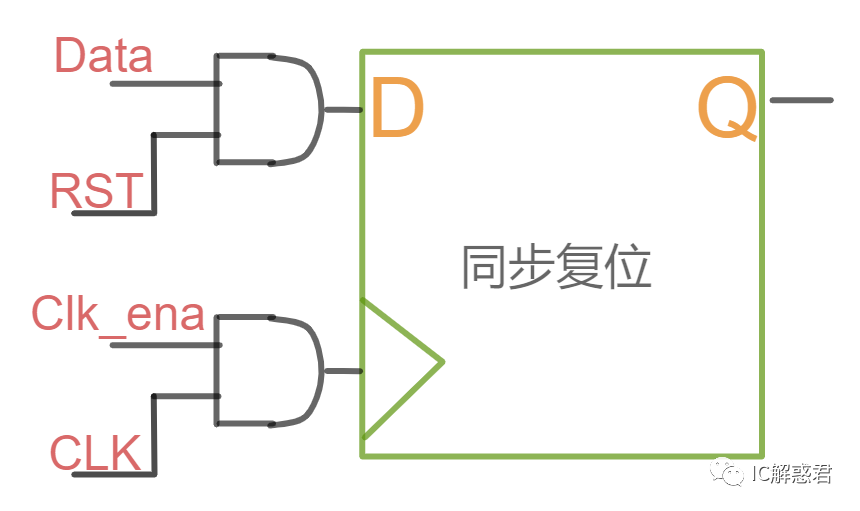

江南体育app(1)在同步复位电路下,复位和数据信号都受到时钟信号的控制,所以同步复位一般可以确保电路是一个

(2)在ASIC设计中,同步电路一般可以综合为更小的同步触发器(因为触发器没有包含复位逻辑),但是在FPGA设计中并不如此,一般FPGA的时序元件为带异步复位的触发器(也有同步触发器,视厂家而定)。如果在FPGA设计中使用同步复位,其消耗的资源相对较多。

(3)由于触发器的跳转只在时钟的边沿,所以触发器可以在一定程度上过滤电路毛刺。进而如果复位由电路内部的逻辑控制,在这种情况下可以在设计中使用同步复位:通过可以在一定程度上过滤电路毛刺的特性,过滤掉内部电路逻辑产生的毛刺,使设计更鲁棒。

(1)同步复位需要较长的保持复位状态时间(最小也要大于时钟周期),保证同步复位信号可以到达每一个寄存器并且要在有效时钟沿之前到达(在真正设计使用的时候还需要考虑时钟偏斜、组合逻辑延时、复位延时等,即:同步复位信号时长>

时钟周期 + 时钟偏斜 + 组合逻辑延时)。

(2)在低功耗设计中,同步复位一般不能用于门控时钟控制的电路。因为同步复位电路中,主要靠时钟驱动复位和数据。当复位发出时,有可能时序电路此时并没有时钟驱动,那么此时的复位就不能完成。

拥有异步复位的寄存器在设计的时候就已经多了一个复位引脚。通过触发该引脚的状态可以在任何时候进行异步复位电路中寄存器。此时异步复位电路的默认优先级为:(复位>

时钟>

数据)(如上上图)。

(1)异步复位的复位逻辑和数据逻辑没有任何关系,所以相比同步复位,能够使数据路径更好地收敛。(上上图对比)

(2)不用在时钟的控制下进行复位,所以对于刚才所提到的低功耗设计中,可以达到无时钟复位的效果[注意:寄存器复位后的正常状态恢复需要时钟参与]。

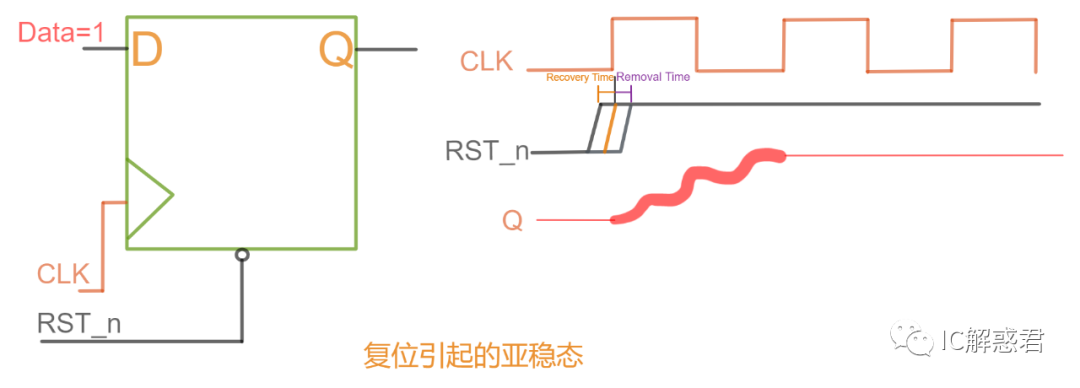

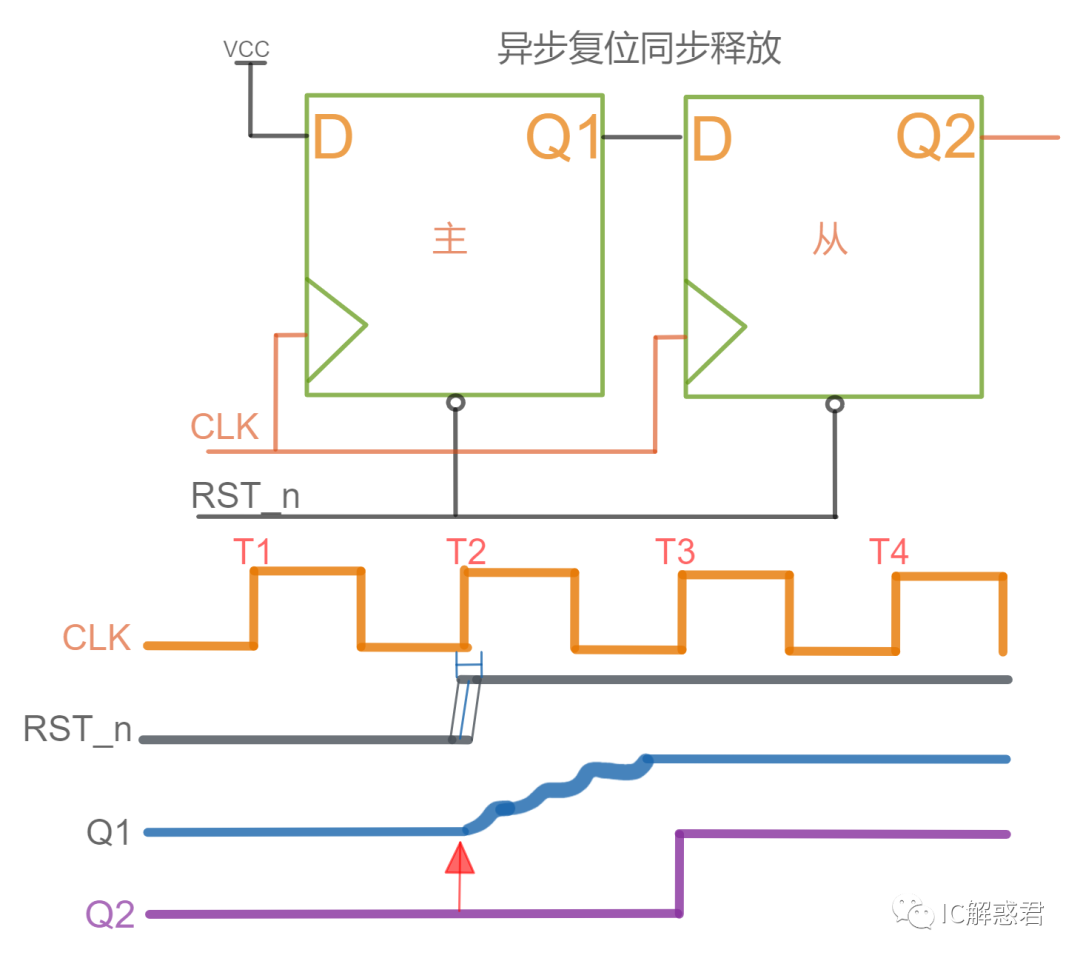

(2)在异步复位的时候,如果释放复位信号在时钟有效边沿周围。那么可能会引起时序单元的输出出现亚稳态,导致电路亚稳态传播。如下图:

对比set up time&hold time和此处的Recovery time &Removaltime,可以发现对于触发器来说,输入信号(Data 和RST_n)都需要对于时钟信号沿保持稳定的一个时间窗口,否则触发器可能会导致亚稳态的输出。为了避免触发器的亚稳态,就需要保证不要在触发器的这几个时间窗内信号有变化。(漫谈STA-setup/hold time)

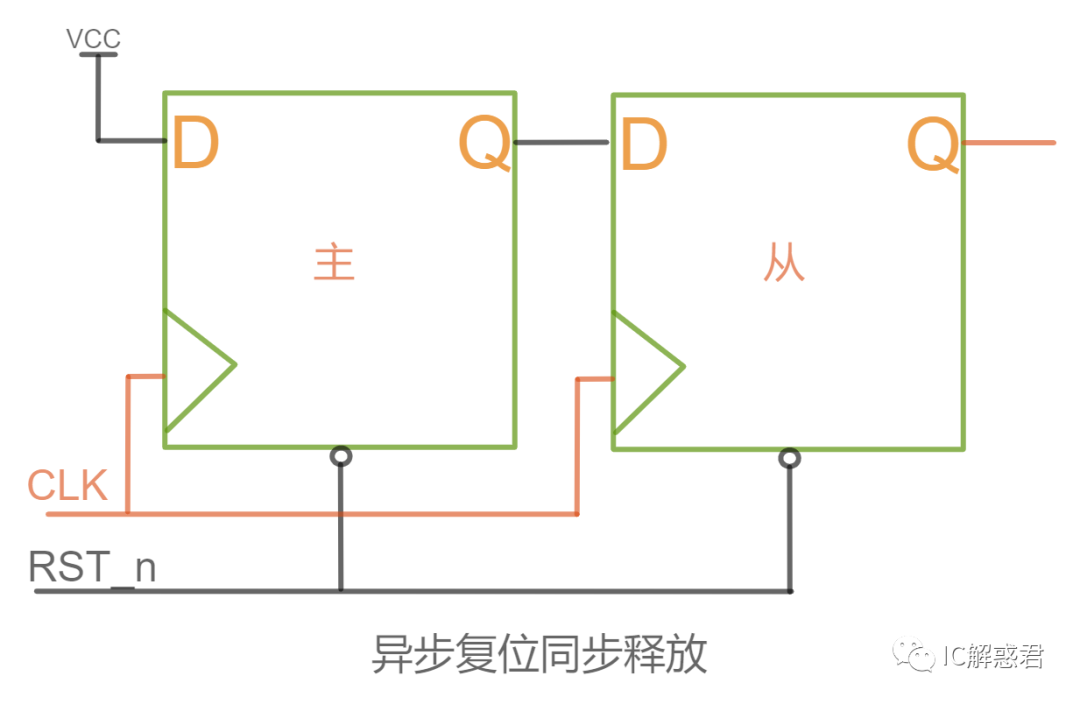

RST_n信号同时复位这两个触发器,这一对触发器的输出信号传输并驱动电路中的其他时序元件完成复位,最后使整个相连接的设计进行复位。

很明显可以看出这两个触发器就是所谓的同步器逻辑。在进行数据跨时钟处理的时候可以通过该同步器逻辑将一个时钟域的信号传输到另一个时钟域。

当复位信号被撤销时:RST_n [0->

1],此时数据VCC将在时钟的控制下进入主触发器。如果此时复位信号被撤销时候恰好碰到时钟的有效沿引起主触发器的亚稳态。但是此时从触发器在时钟控制下江南体育,输入的是主触发器输出的复位稳定值。

如下图:虽然主触发器在T2时刻违背了复位时间窗口,输出了Q1亚稳态的摇摆电平。但是从触发器此时的数据输入接收的还是主触发器输出的Q1稳态的复位状态0。所以从触发器Q2的输出是稳定的复位状态0。在T3时刻主触发器已经从亚稳态状态恢复,输出的是稳定的工作状态电平了(Q1=1)。T3时刻从触发器采样的是稳定的工作状态电平,输出也是稳定的工作状态电平,复位完成。

PS:有同学可能会问,RST_n既然对主触发器违反复位时间窗口,对从触发器来说,也一样违反了时间窗口。那从触发器为什么就没有进入亚稳态呢?

答:对于从触发器来说,RST_n跳变在其复位时钟窗口内,所以违反了从触发器的复位时间窗口,但是从上图可以观察到,从触发器在T2时刻时钟沿的输入为Q1=0,在T1时刻时钟沿的输出为Q2=0,对于从触发器来说,复位前的状态和复位后的状态是一样的。寄存器内部的锁存器不需要跳变来更新自己的状态。所以也就不会因为内部锁存器的电平跳变从而导致亚稳态的发生。

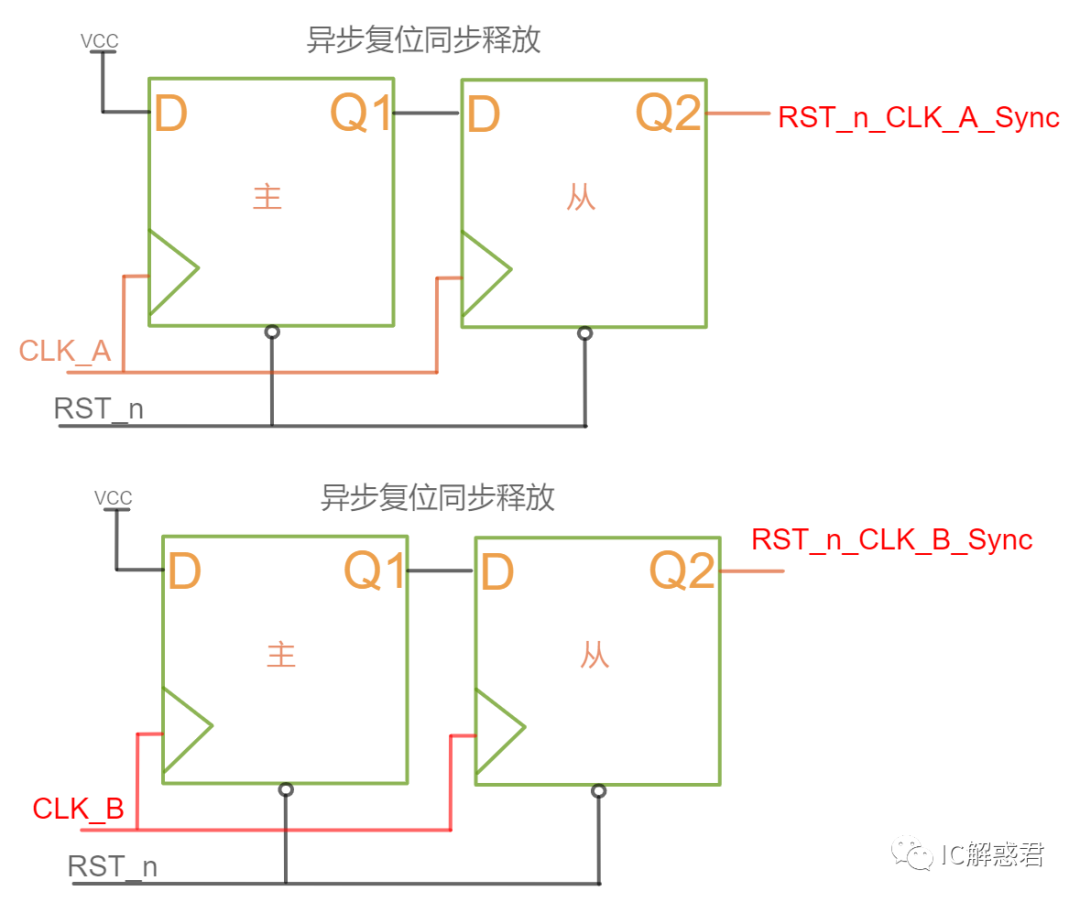

一般来说,完整的一颗SOC芯片内部不止有一个时钟,一般会有多个时钟。所以此时对每一个时钟域下的Reset_n信号都有一套异步复位同步释放逻辑。来保证在自己的时钟域下,复位释放和时钟具有同步的关系,来驱动该时钟域下相关的逻辑和状态的变换等操作。如下图:

为了避免在复位释放的时候引起电路亚稳态,通常采用异步复位同步释放的电路。有效的复位信号可以快速复位相关联的逻辑且不用等待时钟的驱动。同时复位信号经过异步复位同步释放的电路之后,复位信号受到时钟信号的控制(复位信号释放不会在时钟沿的任意点),有效避免了因异步复位信号的移除而引起的电路亚稳态情况的出现。